Something like that for example, and it gives me this. World_DropWargearAtPosition(Game_GetLocalPlayer(),"wargear\\wargear\\campaign\\playable\\race_marine\\sm_arm_terminator_armour",Misc_GetCameraPos()) I've managed to access the dev mod console in the game, and from there I type in. I managed to do this a while back when the game first came out but I haven't been able to do it again, when I just got on for the first time acouple of days ago. I apologize for the inquiry, but I have one small question that I was wondering if you guys could help me with. You can always monitor internal signals on the wave window or log them in your HDL.DOW II: "Fatal Scar Error - Execution Paused" When Dropping Wargear But if you need to drive internal signals then I suggest you have a problem with the design - testbenches should only ever drive the DUT io. With VHDL this requires you to use VHDL 2008. As for driving them, with verilog you can always force/drive any signal within the hierarchy. (use vlog instead of vcom for verilog files).īDF files cannot be simulated, so you can only see what is in the generated HDL file. If you have files a.vhd and b.vhd with the top level entity called "testbench" inside a.vhd, then all you need to do is this in the modelsim console: I suggest driving modelsim yourself and not relying on Quartus to do this for you. This looks like theres files missing in MODELSIM. Problem is, using a testbench, I only see the input/outputs. I know that I can give the signals names, turn the BDF file into a HDL file and then compile it in Modelsim, and then force the signals, but I want to use a testbench to make this be automatic. What could be the problem?Īlso, I would appreciate if you could tell me how to test internal signals of a BDF file in Modelsim using a testbench. I don't understand this problem, just two days ago it didn't happen and now it does.

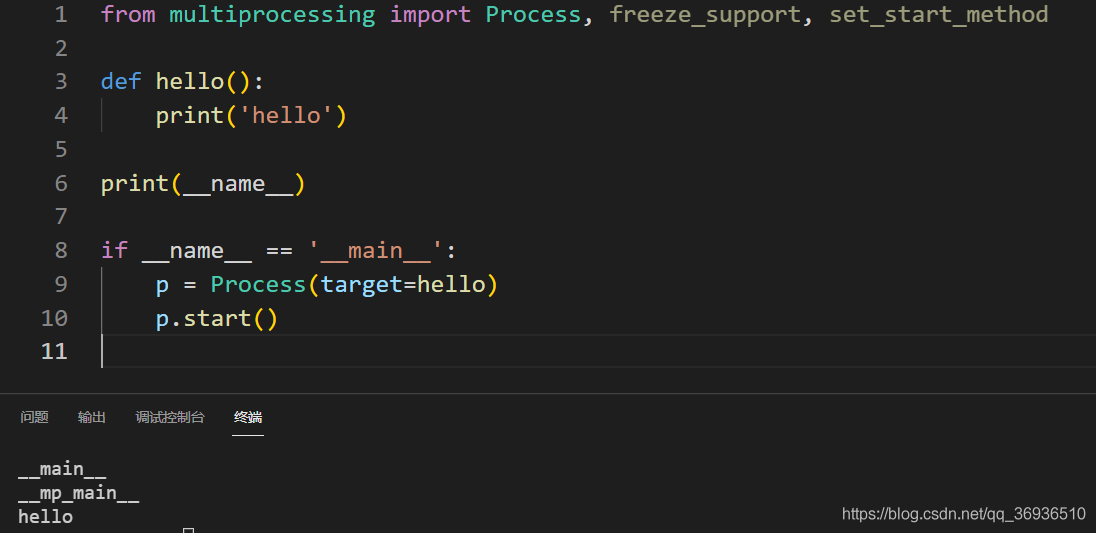

Of course I always made sure to compile whenever I needed to. Tools -> Run simulation tool -> RTL simulation which opened Modelsim. Took to Assignments -> Settings -> EDA tool settings -> Simulation ->Ĭhose compile test bench and chose the VHT file.Ħ. Created a testbench using the Quartus template writer.ĥ. Removed the BDF file from project (did not delete it).ģ. Created a BDF file with two components in it, obviously it has input/output ports and some internal signals.Ģ. Test_run_msim_rtl_vhdl.do PAUSED at line 14ġ. ** Error: (vsim-3170) Could not find 'C:/Users/nettek/QuartusProjects/Final Project - 11.3.16 - par/test/simulation/modelsim/rtl_work.tb_test1'.# Error loading design# Error: Error loading design# Pausing macro execution# MACRO. I am trying to use a small testbench I wrote using the Quartus testbench template writer, but I am getting this error: First I want to say that I searched all the threads here, and while this is a common problem, I could not figure out how to solve it.

0 kommentar(er)

0 kommentar(er)